# CXL-Bridge: CXL controllers for heterogeneous memory architectures Priority Programme "Disruptive Memory Technologies" (SPP 2377) PI: Prof. Dr.-Ing Pramod Bhatotia (TU Munich)

#### Motivation

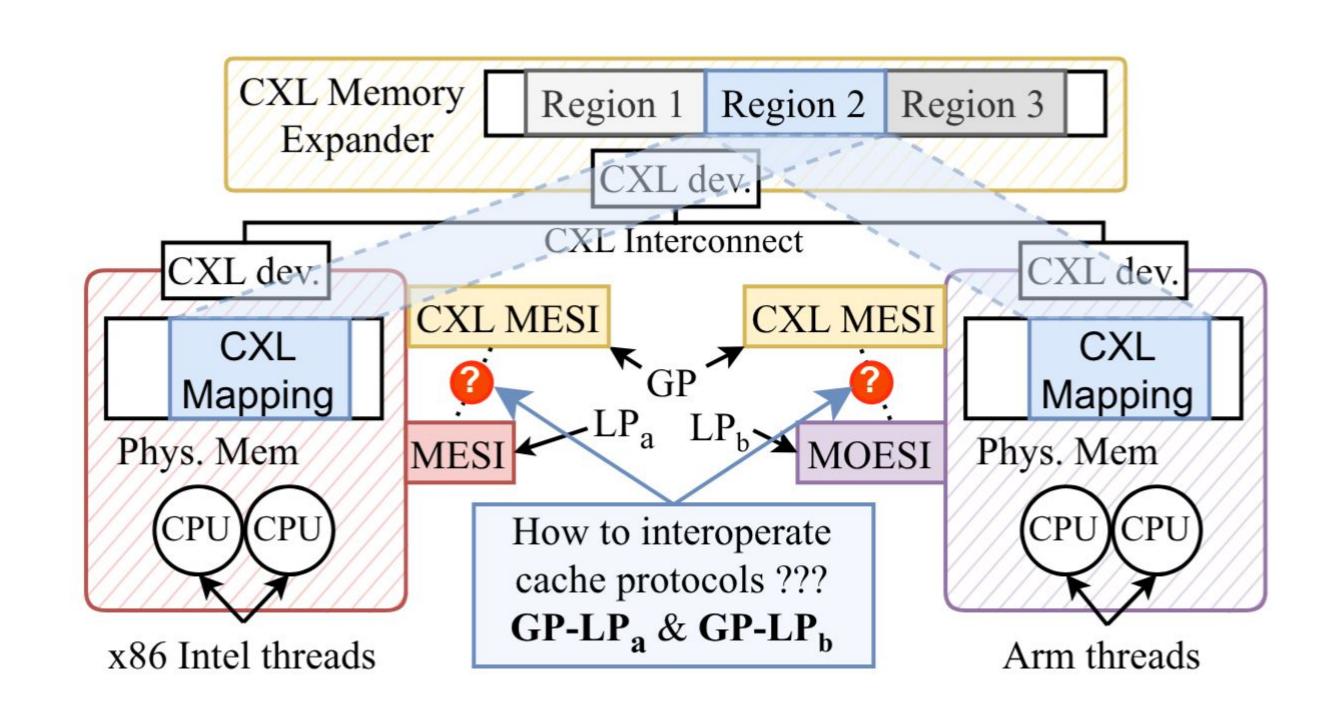

CXL specifications lack safety guarantees for heterogeneous & multi-host shared memory

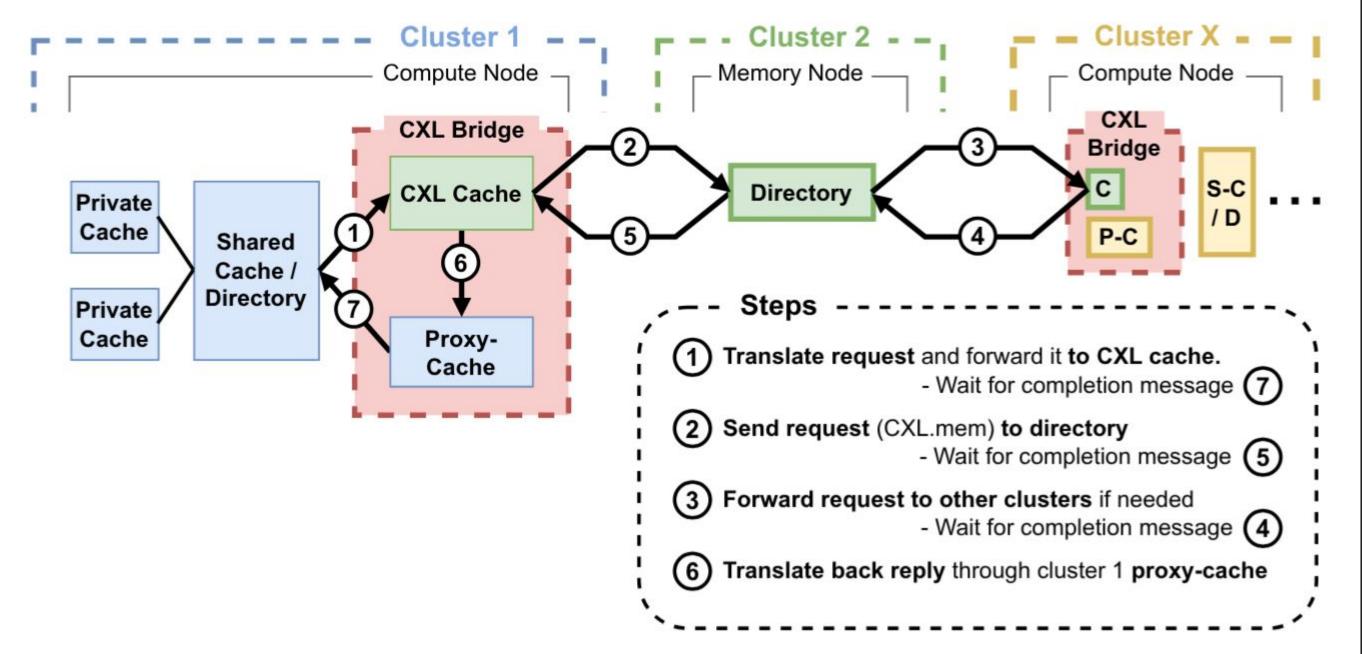

#### CXL Bridge Controllers

- Approach: Non-intrusively <u>interoperate</u> local (host-specific) protocols with CXL.mem global protocol

- Problem: <u>Semantic gap</u> between host protocols (requests/responses) and CXL specifications

- Solution: A new CXL Bridge abstraction

- Key Ideas: an "interface" controller

- translate and propagate coherence transactions between protocols

- dedicated controller with new state machine built from protocol specs

#### Problem statement

How to systematically integrate CXL distributed coherence into heterogeneous hardware architectures?

#### **CXL** Bridges

Push-button *synthesis* and *verification* of heterogeneous CXL coherence controllers

No coherence overheads

- Traffic (bandwidth)

- Network delays (latency)

- Formal verification

Correctness

- Automated

- Correctness criteria

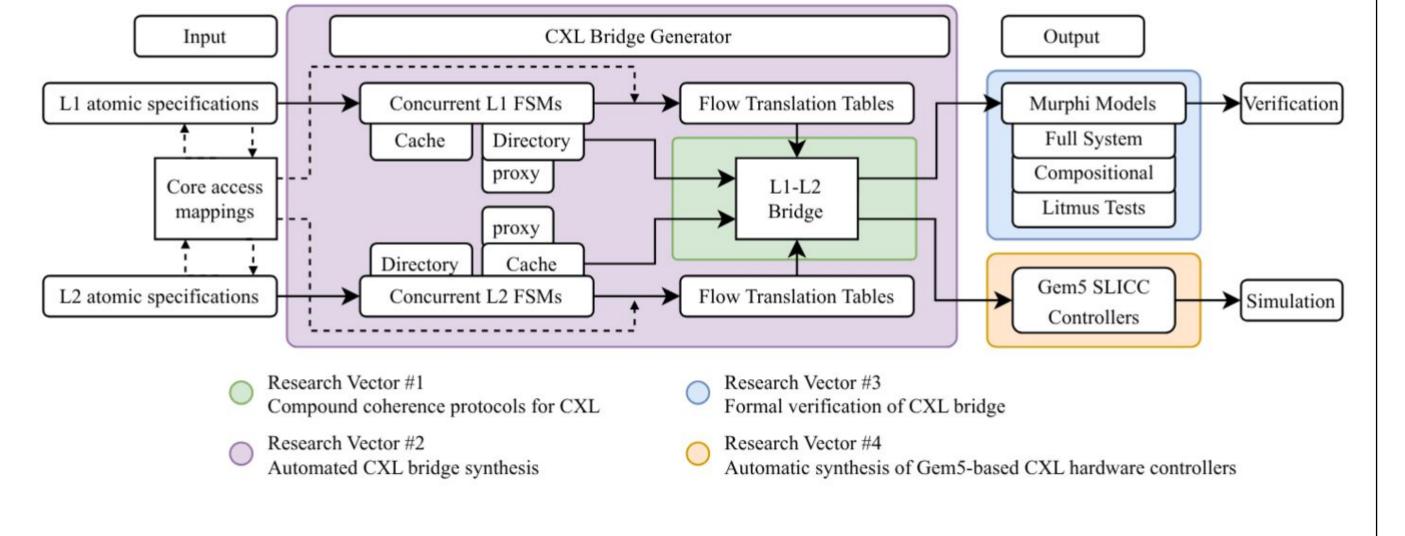

# <u>Automated Synthesis</u> of CXL Bridge Controller Synthesis

- Approach: Universal methodology to construct CXL bridges

- Problem: Complexity of protocol compounding (multiplicative #states/#transitions), need to evolve fast with new specs

- Solution: Specification-driven synthesis of CXL Bridge

- Key Ideas:

- Input <u>machine readable specifications</u> of both protocols at the interface

- Derive bridge state machines from the protocol IRs

- Output <u>verification and simulation models</u> with 2 codegen backends

#### CXL Heterogeneous Memory Consistency

- Approach: A <u>correctness criteria</u> for CXL heterogeneous shared memory

- Problem: Formally define the <u>Memory</u>

Consistency Model (MCM) of CXL bridges

- "What happens when concurrent threads access the same memory with different memory models? e.g., TSO & ARM"

- Solution: Formally show that CXL bridges realize Compound Memory Models

- Every node can view and use the shared memory as if it were its local (native) MCM

- No code change (source or compiled)

| $T_1$ (TSO)               | $T_2$ (RC)                | $T_1$ (RC)                | $T_2$ (TSO)                        |

|---------------------------|---------------------------|---------------------------|------------------------------------|

| $st_1$ : st #1 $X$ ;      | $ld_1$ : ldar $r_1$ $Y$ ; | $st_1$ : st #1 $X$ ;      | $d_1$ : ld $r_1$ $Y$ ;             |

|                           |                           |                           | $m_1$ : mfence:                    |

| $st_2$ : st #1 $Y$ ;      | $ld_2$ : ld $r_2$ $X$ ;   | $st_2$ : stlr #1 $Y$ ;    | $  ld_2: \operatorname{ld} r_2 X;$ |

| TSO producer, RC consumer |                           | RC producer, TSO consumer |                                    |

Heterogeneous MP litmus test. In both,  $st1 \rightarrow st2 \& ld1$   $\rightarrow ld2$ , thus, the outcome  $\{r1 = 0, r2 = 1\}$  is disallowed.

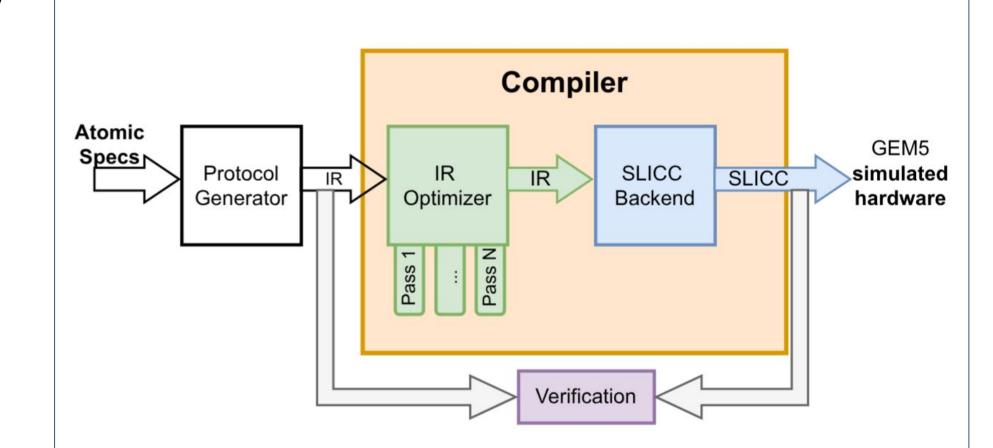

### Performance assessment: Gem5-based CXL Bridges

- Approach: Gem5-based simulations to assess performance of CXL bridges

- Problem: <u>inflexible development</u> of cache coherence controllers in Gem5 (SLICC DSL)

- Solution: A <u>compilation framework</u> to generate SLICC code from <u>CXL Bridge IR</u>

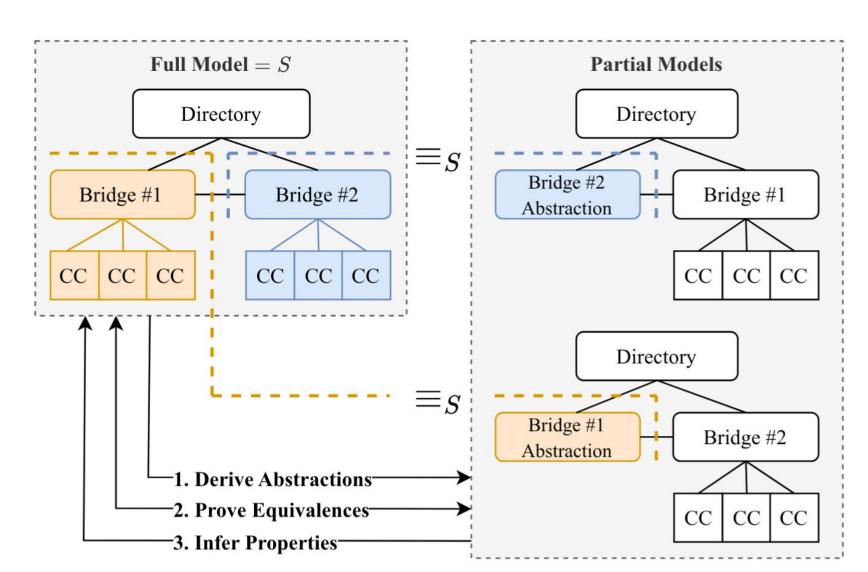

## Formal Verification of Coherence Protocols

- Verification properties from any state

- <u>Safety:</u> no compound MCM violation (litmus tests)

- <u>Liveness:</u> core eventually get any requested access

- Approach: Explicit state model checking

- Problem: state space explosion (<u>OoM</u>)

- Solution: compositional system models