# DRAMaOS: **DRAM-a**ware **OS**

Illia Ostapyshyn Nils Wilbert

### Matthias Jung

### Daniel Lohmann

### Breaking the Barrier Between OS and HW Memory Management

**Problem:** Modern DRAM is increasingly complex and gains new features, but the existing hardware and software lack support to unleash its full potential.

### Solution:

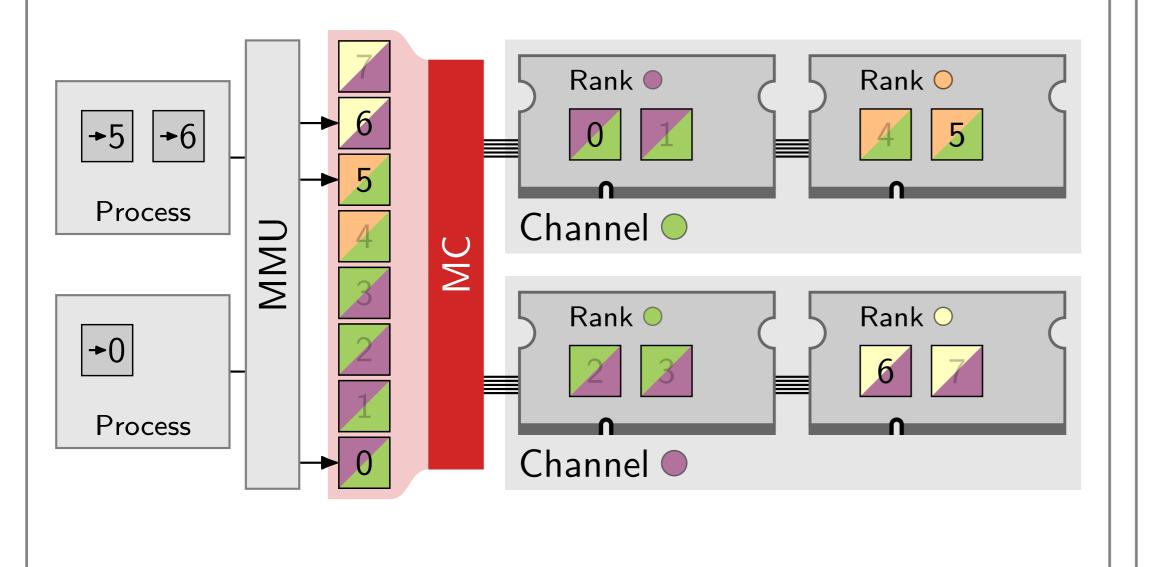

- OS becomes aware of the DRAM's internal structure to manage it effectively.

- Smart memory controller exposes control and performs simple tasks autonomously.

#### Example: Power Management Effect of defragmentation effort by granularity Available power management features ■ (☑) supported (optional) ■ with retention ■ accessible **DDR LPDDR** Granularity Power mode **HBM** Allocated memory is 2 3 4 scattered over time Full power off Channel Self refresh Channel Free blocks [%] Existing features apply to **MPSM** Channel coarse granularities MPSM (DDR5) Rank Power-Down Rank Suitable compaction **PASR** 1/8 Rank must be cost-aware 1/8 Rank **PARC** 256K 128M Efficiency mode 32K Subchannel Block size

### Improved OS Memory Management

**Problem:** Current memory management is based on outdated beliefs

- 1. Only used memory is good memory (cache 'em all)

- 2. All frames are equal (no external fragmentation)

Our Belief: OS must be aware and in control of DRAM's capabilities.

- Page cache actually costs energy and therefore money

- Targeted allocation can increase performance and security/safety

- → Reflect DRAM capabilities and memory slices they affect in the memory management structures and policies of the OS.

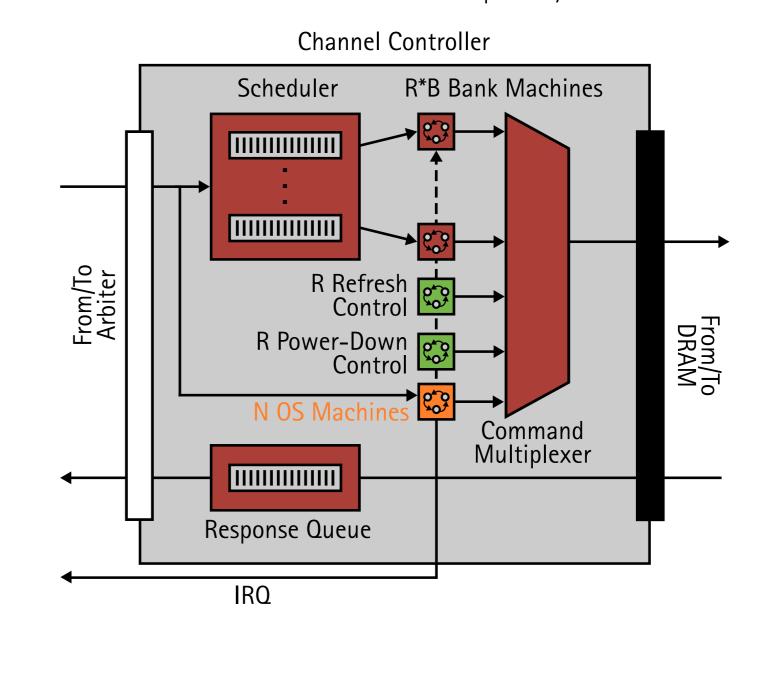

## Smart Memory Controller

**Problem:** Traditional DRAM Memory Controllers (MC)

- 1. Are non-programmable

- 2. Can only use locally buffered requests to perform optimizations

- 3. Do not expose DRAM internals to OS/software stack

Our Proposal: Add programmable OS machines to the MC.

- OS can offload tasks to the MC

- Explore different levels of OS-machine complexity

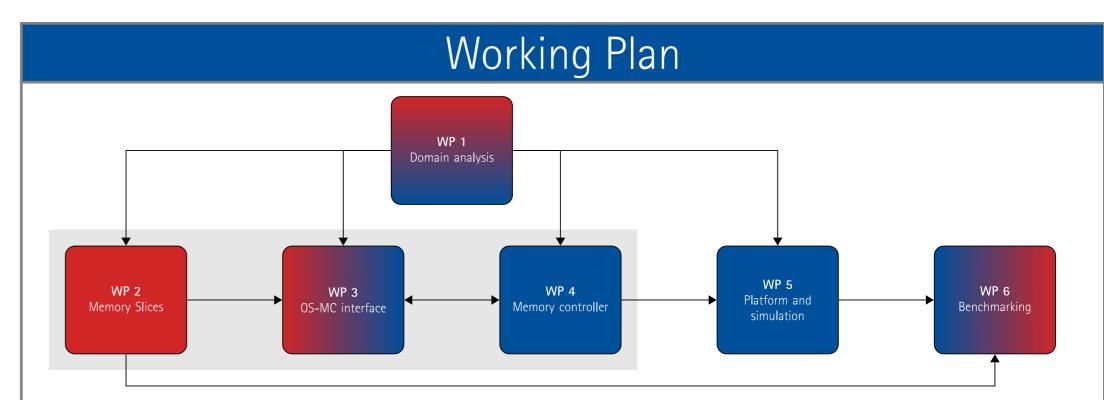

### Virtual Platform

DRAMSys<sup>5.0</sup>

DRAMSys

gem5

- Cycle-accurate DRAM simulator for all JEDEC standards

- Fast TLM-level simulation

- Includes power model and trace analyzer

- Available on https://github.com/tukl-msd/DRAMSys

gem5

Full-system simulator capable of booting Linux

Our Framework: Couple DRAMSys with gem5 to create a fast and flexible simulation platform supporting our proposed OS-MC codesign.

**Role within the SPP:** Cross-domain project combining HW simulation and OS areas, allowing for great cooperation potential.

**Systems Research and Architecture**

https://sra.uni-hannover.de

Leibniz

Universität

Hannover

**Computer Engineering**

567410490 JU 3158/1-1, LO 1719/10-1